#### About this Manual

We've added this manual to the Agilent website in an effort to help you support your product. This manual is the best copy we could find; it may be incomplete or contain dated information. If we find a more recent copy in the future, we will add it to the Agilent website.

#### **Support for Your Product**

Agilent no longer sells or supports this product. Our service centers may be able to perform calibration if no repair parts are needed, but no other support from Agilent is available. You will find any other available product information on the Agilent Test & Measurement website, <a href="https://www.tm.agilent.com">www.tm.agilent.com</a>.

#### **HP References in this Manual**

This manual may contain references to HP or Hewlett-Packard. Please note that Hewlett-Packard's former test and measurement, semiconductor products and chemical analysis businesses are now part of Agilent Technologies. We have made no changes to this manual copy. In other documentation, to reduce potential confusion, the only change to product numbers and names has been in the company name prefix: where a product number/name was HP XXXX the current name/number is now Agilent XXXX. For example, model number HP8648A is now model number Agilent 8648A.

# HP E2443B Intel Pentium CPU Preprocessor Interface User's Guide

for the HP 1660A, HP 16540/16541A,D and HP 16550A Logic Analyzers

©Copyright Hewlett-Packard Company 1993

Manual Part Number E2443-90903 Microfiche Part Number E2443-90803

Printed in U.S.A. April 1993

#### **Printing History**

New editions are complete revisions of the manual. Update packages, which are issued between editions, contain additional and replacement pages to be merged into the manual by the customer. The dates on the title page change only when a new edition is published.

A software code may be printed before the date; this indicates the version of the software product at the time the manual or update was issued. Many product updates and fixes do not require manual changes and, conversely, manual corrections may be done without accompanying product changes. Therefore, do not expect a one to one correspondence between product updates and manual updates.

Edition 1 April 1993 E2443-90903

### **List of Effective Pages**

The List of Effective Pages gives the date of the current edition and of any pages changed in updates to that edition. Within the manual, any page changed since the last edition is indicated by printing the date the changes were made on the bottom of the page. If an update is incorporated when a new edition of the manual is printed, the change dates are removed from the bottom of the pages and the new edition date is listed in the Printing History and on the title page.

Pages Effective Date

### Product Warranty

This Hewlett-Packard product has a warranty against defects in material and workmanship for a period of 1 year from date of shipment. During warranty period, Hewlett-Packard Company will, at its option, either repair or replace products that prove to be defective.

For warranty service or repair, this product must be returned to a service facility designated by Hewlett-Packard. However, warranty service for products installed by Hewlett-Packard and certain other products designated by Hewlett-Packard will be performed at Buyer's facility at no charge within the Hewlett-Packard service travel area. Outside Hewlett-Packard service travel areas, warranty service will be performed at Buyer's facility only upon Hewlett-Packard's prior agreement and Buyer shall pay Hewlett-Packard's round trip travel expenses.

For products returned to Hewlett-Packard for warranty service, the Buyer shall prepay shipping charges to Hewlett-Packard and Hewlett-Packard shall pay shipping charges to return the product to the Buyer. However, the Buyer shall pay all shipping charges, duties, and taxes for products returned to Hewlett-Packard from another country.

Hewlett-Packard warrants that its software and firmware designated by Hewlett-Packard for use with an instrument will execute its programming instructions when properly installed on that instrument.

Hewlett-Packard does not warrant that the operation of the instrument, software, or firmware will be uninterrupted or error-free.

### Limitation of Warranty

The foregoing warranty shall not apply to defects resulting from improper or inadequate maintenance by the Buyer, Buyer-supplied software or interfacing, unauthorized modification or misuse, operation outside of the environmental specifications for the product, or improper site preparation or maintenance.

NO OTHER WARRANTY IS EXPRESSED OR IMPLIED. HEWLETT-PACKARD SPECIFICALLY DISCLAIMS THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE.

### **Exclusive** Remedies

THE REMEDIES PROVIDED HEREIN ARE BUYER'S SOLE AND EXCLUSIVE REMEDIES. HEWLETT-PACKARD SHALL NOT BE LIABLE FOR ANY DIRECT, INDIRECT, SPECIAL, INCIDENTAL, OR CONSEQUENTIAL DAMAGES, WHETHER BASED ON CONTRACT, TORT, OR ANY OTHER LEGAL THEORY.

#### **Assistance**

Product maintenance agreements and other customer assistance agreements are available for Hewlett-Packard products.

For assistance, contact your nearest Hewlett-Packard Sales and Service Office.

#### Certification

Hewlett-Packard Company certifies that this product met its published specifications at the time of shipment from the factory. Hewlett-Packard further certifies that its calibration measurements are traceable to the United States National Bureau of Standards, to the extent allowed by the Bureau's calibration facility, and to the calibration facilities of other International Standards Organization members.

#### Safety

This product has been designed and tested according to International Safety Requirements. To ensure safe operation and to keep the product safe, the information, cautions, and warnings in this user's guide must be heeded.

### **Contents**

#### Introduction

Logic Analyzer Software Requirement Logic Analyzers Supported How to Use This Manual

| Chapter 1: | Setting Up the HP E2443B              |      |

|------------|---------------------------------------|------|

| •          | Introduction                          | 1-   |

|            | Duplicating the Master Disk           |      |

|            | Equipment Supplied                    |      |

|            | Minimum Equipment Required            |      |

|            | Installation Quick Reference          |      |

|            | Setting the Switches and Jumpers      |      |

|            | Mode of Operation                     |      |

|            | Clock Qualifier Inputs                |      |

|            | Clock Version (Timing Only)           |      |

|            | Connecting to the Target System       |      |

|            | Connecting to the HP E2443B           |      |

|            | Power Up / Down Sequence              |      |

|            | Setting Up the Analyzer from the Disk |      |

|            | Timing Analysis                       |      |

|            |                                       |      |

|            |                                       |      |

| Chapter 2: | Analyzing the Intel Pentium CPU       |      |

|            | Introduction                          | 2-   |

|            | Format Specification                  |      |

|            | Symbols                               |      |

|            | Additional Symbols                    |      |

|            | Listing Menu                          |      |

|            | Burst and Cacheable Data              |      |

|            | The Pentium CPU Inverse Assemblers    |      |

|            | Address Labels                        | 2-14 |

|            | Prefetched Instructions               | 2-1: |

|            | Synchronizing the Inverse Assembler   |      |

|            | Operand Size                          |      |

|            | Byte Enable Validity                  |      |

|            | Incomplete Decoding                   |      |

|            | Opcode Data Numeric Bases             |      |

|            | Branch Trace Messaging                |      |

Contents-1

|             | Illegal Instructions2-17The IAPENTE Inverse Assembler2-18Show/Suppress2-19Code Synchronization2-19IDT Description2-19Modes of Operation2-20Qualified / Non-qualified Clocking2-20ClkQual2-21State Waveforms Using State-Per-Clock Mode2-23 |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Chapter 3:  | General Information                                                                                                                                                                                                                        |

| Onapier 3.  |                                                                                                                                                                                                                                            |

|             | Introduction                                                                                                                                                                                                                               |

|             | Characteristics                                                                                                                                                                                                                            |

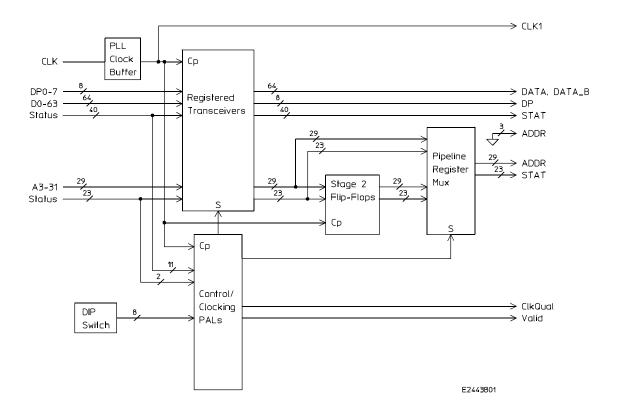

|             | Interface Description                                                                                                                                                                                                                      |

|             | Clocking                                                                                                                                                                                                                                   |

|             | Pentium CPU Signal to HP E2443B Connector Mapping3-5                                                                                                                                                                                       |

|             | Servicing                                                                                                                                                                                                                                  |

| Appendix A: | Troubleshooting                                                                                                                                                                                                                            |

| пропакт.    | Target Board Will Not Bootup                                                                                                                                                                                                               |

|             | Bent Pins A-1                                                                                                                                                                                                                              |

|             | "Slow or Missing Clock"                                                                                                                                                                                                                    |

|             | Slow Clock                                                                                                                                                                                                                                 |

|             | "No Configuration File Loaded"                                                                                                                                                                                                             |

|             | "Selected File is Incompatible"                                                                                                                                                                                                            |

|             | " Inverse Assembler Not Found"                                                                                                                                                                                                             |

|             | No Inverse Assembly A-3                                                                                                                                                                                                                    |

|             | Incorrect Inverse Assembly                                                                                                                                                                                                                 |

|             | No Activity on Activity Indicators                                                                                                                                                                                                         |

|             | Capacitive Loading A-4                                                                                                                                                                                                                     |

|             | Unwanted Triggers A-4                                                                                                                                                                                                                      |

|             | "Waiting for Trigger" A-4                                                                                                                                                                                                                  |

|             | Intermittent Data Errors A-4                                                                                                                                                                                                               |

|             | "Time from Arm Greater Than 41.93 ms." A-4                                                                                                                                                                                                 |

|             | No Setup/Hold Field on Format Screen A-4                                                                                                                                                                                                   |

|             | "Default Calibration Factors Loaded" (16540/16541A,D) A-4                                                                                                                                                                                  |

Contents-2

### Introduction

The HP E2443B Preprocessor Interface provides a complete interface for state or timing analysis of a Pentium™ CPU target system by an HP 1660A, HP 16540/16541A,D, or HP 16550A Logic Analyzer.

The Pentium CPU configuration software on the flexible disk sets up the format specification menu of the logic analyzer for compatibility with the Pentium microprocessor. It also loads the inverse assembler for obtaining displays of Pentium CPU data in Pentium CPU assembly language mnemonics.

### Logic Analyzer Software Requirement

The HP E2443B Preprocessor Interface requires HP 16500A system and module software version V05.03 or higher (HP 16540/16541A,D and HP 16550A Logic Analyzers). For the HP 16500B mainframe, system and module software version V01.00 or higher is required. For the HP 1660A Logic Analyzer, software version V01.00 or higher is required. To use the enhanced inverse assembler with the HP 1660A Logic Analyzer, software version V02.00 or higher is required. If your software version is older than those listed above, load new system software with the above version numbers or higher before loading the HP E2443B software.

Pentium™ is a trademark of Intel Corporation.

Introduction-1

### Logic Analyzers Supported

The following logic analyzers are supported by the HP E2443B:

#### **HP 1660A**

The HP 1660A Logic Analyzer provides 4 k of memory depth with 136 channels of 100 MHz state analysis or 250 MHz timing analysis. This logic analyzer also supports various combinations of mixed state/timing analysis.

#### HP 16540A,D with three HP 16541A,D Expansion Cards

This logic analyzer combination provides 4 k of memory depth (16 k with the D version) with 160 channels of 100 MHz state or timing analysis.

#### HP 16550A (two cards)

This logic analyzer provides 4 k of memory depth with 102 channels per card of 100 MHz state analysis or 250 MHz timing analysis. This logic analyzer also supports various combinations of mixed state/timing analysis.

### How to Use This Manual

This manual is organized into three chapters and one appendix:

- Chapter 1 explains how to install and configure the HP E2443B Preprocessor Interface for state or timing analysis with the supported logic analyzers.

- Chapter 2 provides reference information on the format specification and symbols configured by the HP E2443B software. It also provides information about the inverse assemblers and status encoding.

- Chapter 3 contains additional reference information including the characteristics and signal mapping for the HP E2443B Preprocessor Interface. It also contains information on servicing.

- Appendix A contains information on troubleshooting problems or difficulties which may occur with the preprocessor interface.

#### Introduction-2

### **Setting Up the HP E2443B**

#### Introduction

This chapter explains how to install and configure the HP E2443B Preprocessor Interface for state or timing analysis with the HP 1660A, HP 16540/16541A,D or HP 16550A Logic Analyzers.

### **Duplicating the Master Disk**

Before you use the HP E2443B software, use the Duplicate Disk operation in the disk menu of your logic analyzer to make a duplicate copy of the HP E2443B master disk. Store the master disk in a safe place and use the back-up copy to configure your logic analyzer. This will help prevent the possibility of losing or destroying the original files in the event the disk wears out, is damaged, or a file is accidentally deleted.

### **Equipment** Supplied

The HP E2443B Preprocessor Interface consists of the following equipment:

- The preprocessor interface hardware, which includes the preprocessor interface circuit card and cables.

- The configuration and inverse assembly software on a 3.5-inch disk.

- Two additional jumpers (HP part number 1252-3743).

- This user's guide.

### Note

The preprocessor interface socket assembly pins are covered at the time of shipment with either a conductive foam wafer or a conductive plastic pin protector. This is done to protect the delicate gold plated pins of the assembly from damage due to impact.

When you're not using the preprocessor interface, protect the socket assembly pins from damage by covering them with the foam or plastic pin protector.

HP E2443B Pentium CPU Preprocessor Interface Setting Up the HP E2443B

### Minimum Equipment Required

The minimum equipment required for analysis of a Pentium CPU target system consists of the following:

- An HP 1660A, HP 16540A,D with three HP 16541A,D Expansion Cards, or an HP 16550A (two cards).

- The HP E2443B Preprocessor Interface, which includes the configuration files and inverse assemblers.

### Installation Quick Reference

The following procedure describes the major steps required to perform measurements with the HP E2443B Preprocessor Interface. The page numbers listed in the various steps refer you to sections in this manual that offer more detailed information.

To prevent equipment damage, be sure to remove power from the target system whenever the preprocessor interface or microprocessor is being connected or disconnected.

- 1. Set the switches and jumpers according to your measurement requirements (see page 1-3).

- 2. Install the preprocessor interface in the target system (page 1-7).

- 3. Connect the logic analyzer probes to the cable connectors of the preprocessor interface as listed in table 1-3 (see page 1-10).

- 4. Load the appropriate logic analyzer configuration file. This also loads the appropriate default inverse assembler file (page 1-11).

- 5. If you want to fully capture the execution trace, disable the cache. If possible, you may also want to disable page translation, so the physical addresses the preprocessor interface monitors are effectively the logical addresses (see page 1-8).

Do not disable the cache memory if burst transfers are to be monitored. Enabling the cache memory will allow you to view the data coming across the bus, but the code may not be properly disassembled. Also, when the cache is enabled, unexecuted prefetches are not inferred, and the unexecuted prefetch markers are not displayed.

Setting Up the HP E2443B 1-2

HP E2443B Pentium CPU Preprocessor Interface

### Setting the Switches and Jumpers

The HP E2443B can capture Pentium CPU data in four modes: Timing, State-Per-Clock, State-Per-Transfer, and Debugger modes. Switches 1 and 2 allow you to select the **mode** of operation.

For State-Per-Clock mode, you can also have qualified or non-qualified clocking (selected through the Format menu). State-Per-Transfer and Debugger modes only work in qualified clocking. Switches 3 to 8 select the **clock qualifier inputs** for qualified clocking.

In the Timing mode, you can select a buffered version of the microprocessor clock or a phase-locked loop version. The **clock version** is determined by the location of the jumper on the 1 x 3 header.

#### **Mode of Operation**

In Timing mode, the signals are buffered, but otherwise passed straight through to the logic analyzer. In State-Per-Clock mode, all signals are latched by CLK, and clocked into the logic analyzer each CLK cycle (see Chapter 2 for additional information on State-Per-Clock). In State-Per-Transfer mode, address pipelining is realigned, and only valid transfers are clocked into the logic analyzer. Debugger mode is identical to State-Per-Transfer mode with the exception that, whenever IU, IV or IBT are asserted, data is captured regardless of whether or not it is valid.

Switches 1 and 2 determine the mode of operation (see table 1-1). The LED on the HP E2443B indicates the selected mode of operation.

Switch 2 Switch 1 **Mode of Operation LED Color** Off State-Per-Transfer Off Green State-Per-Clock Off On Amber On Off Timing Red On Off On Debugger

Table 1-1. Switch 1 and 2 Settings (Mode of Operation)

### Clock Qualifier Inputs

In qualified clocking, the level of a clock qualifier (ClkQual) is ANDed with the edge of the clock (Clk1 on the HP E2443B pod P1), and the resultant rising edge clocks information into the logic analyzer. The clock qualifier equations are listed in Chapter 2.

The logic analyzer must be clocked as qualified for State-Per-Transfer and Debugger modes; it can be clocked as qualified or non-qualified for State-Per-Clock mode.

Note that for State-Per-Clock mode, qualified clocking decreases the number of invalid data/code states which are clocked into the logic analyzer, since only Clk1 ↑ edges that occur when ClkQual is asserted will be clocked into the logic analyzer. The configuration files set up the logic analyzers for qualified clocking. Use the Format menu to configure the logic analyzer for non-qualified clocking (see Chapter 2).

Switches 3 - 8 select the inputs to the clock qualifier. These switches allow you to select particular cycles or operations to be clocked into the logic analyzer. The inputs to the clock qualifier are selected by closing the appropriate switches. For all switches which are closed, the signals are ORed together to create ClkQual; therefore, closing additional switches increases the variety of states which are clocked into the logic analyzer.

The different clock qualifier inputs are relevant only for certain modes of operation (see table 1-2). For the modes marked "no", the switch position has no effect.

Note that for State-Per-Transfer and Debugger modes, when HLDA or BOFF# is asserted, the preprocessor interface automatically switches to State-Per-Clock mode, regardless of the switch 7 and 8 settings. The State-Per-Clock ClkQual signal becomes relevant. If none of the clock qualifier inputs are selected, then no information will be clocked into the logic analyzer. When HLDA or BOFF# is deasserted, the preprocessor interface automatically switches back to State-Per-Transfer or Debugger mode.

Table 1-2. Switch 3 - 8 Settings (Clock Qualifier Inputs)

| Relevant for Mode of<br>Operation | Switch 3<br>BRDY# | Switch 4<br>BRDYC# | Switch 5<br>ADS# | Switch 6<br>EADS# | Switch 7<br>HLDA | Switch 8<br>BOFF# |

|-----------------------------------|-------------------|--------------------|------------------|-------------------|------------------|-------------------|

| Timing                            | yes               | yes                | yes              | yes               | yes              | yes               |

| State-Per-Clock                   | yes               | yes                | yes              | yes               | yes              | yes               |

| * State-Per-Transfer              | no                | no                 | no               | yes ***           | **               | **                |

| * Debugger                        | no                | no                 | no               | yes ***           | **               | **                |

- \* In State-Per-Transfer and Debugger modes, the preprocessor-generated signal "Valid" is also ORed into ClkQual; therefore, valid data-transfer states are always captured. In Debugger mode, all states in which IU, IV, or IBT are asserted are also captured. Valid = ![!(BRDY# & BRDYC#) & (Pentium CPU in T2, T12, T2P states)]

- \*\* During State-Per-Transfer and Debugger modes, when HLDA or BOFF# is asserted, the preprocessor interface automatically switches to State-Per-Clock mode, regardless of the switch 7 and 8 settings. The State-Per-Clock clock qualifier inputs become relevant. The HLDA or BOFF# data is not disassembled. When HLDA or BOFF# is deasserted, the preprocessor interface switches back to State-Per-Transfer or Debugger mode; therefore, all other data is still aligned and disassembled.

- \*\*\* For State-Per-Transfer and Debugger modes, pipelined addresses are realigned. The address captured with EADS# is the address of the current bus cycle; it is not the inquire address. However, cache writebacks which are triggered by a snoop will be captured and displayed. To fully capture inquire cycle activity, use State-Per-Clock mode.

### Clock Version (Timing Only)

The 1 x 3 header serves as a single-pole double-throw switch. It allows you to select the version of the clock which is sent to the logic analyzer in Timing mode. One version of the clock (PLL) is routed through a phase-locked loop, while the other version (CLK) is only buffered. The rising edges of CLK and PLL line up within  $-0.6\pm.1$  ns, with PLL leading CLK. The factory setting for the jumper is with PLL selected. For more precise timing analysis of the clock signal, the jumper can be moved to the CLK position, so that the buffered version of the clock is captured. The position of this jumper is only relevant for Timing mode.

The load on the clock signal is increased by one 74FCT646A input when the jumper is in the CLK position.

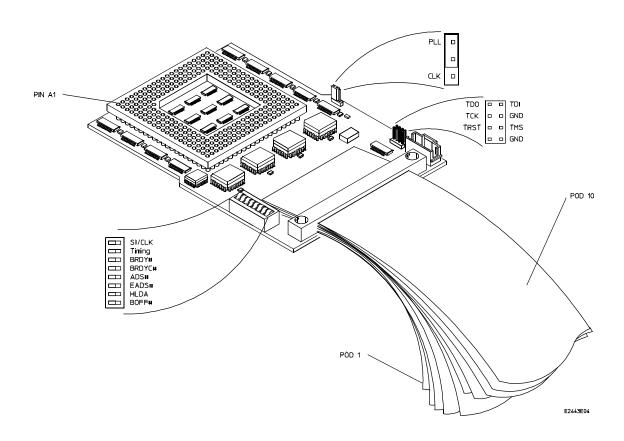

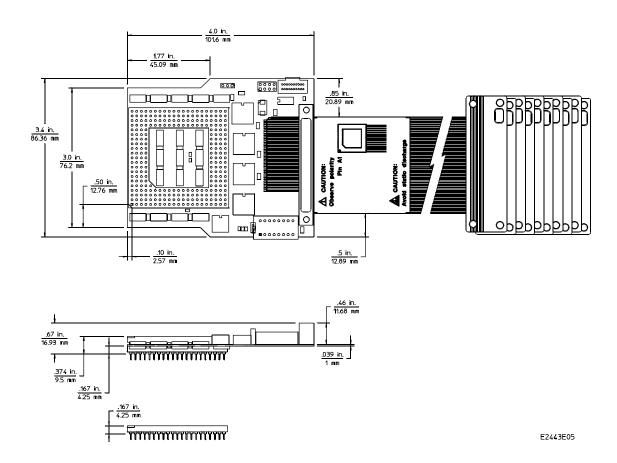

Figure 1-1. Preprocessor Interface Assembly

# Connecting to the Target System

The following steps explain how to connect the HP E2443B Preprocessor Interface to your target system:

Caution

To prevent equipment damage, be sure to remove power from the target system whenever the preprocessor interface or microprocessor is being connected or disconnected.

1. Remove the Pentium microprocessor from its socket on the target system and store it in a protected environment.

Serious damage to the target system or preprocessor interface can result from incorrect connection. Note the position of pin A1 (figure 1-1) on the preprocessor interface connector and the target system socket prior to inserting the connector in the socket. Also, take care to align the preprocessor interface connector with the socket on the target system so that all microprocessor pins are making contact.

2. Plug the preprocessor interface connector into the microprocessor socket on the target system.

If the preprocessor interface connector interferes with components of the target system or if a higher profile is required, additional plastic pin guards can be added. Plastic pin guards can be ordered from Hewlett-Packard using the part number 1200-1753. However, any 273-pin PGA IC socket with a Pentium CPU footprint and gold-plated pins can be used.

3. Plug the Pentium microprocessor into the socket of the preprocessor interface board. The socket on the preprocessor interface board is designed with low-insertion-force pins to allow you to install or remove the microprocessor with a minimum amount of force.

HP E2443B

Pentium CPU Preprocessor Interface

Setting Up the HP E2443B

Care must be used when removing a microprocessor or socket from the preprocessor interface board to prevent damaging the traces on the board.

4. If you want to fully capture the execution trace, disable the cache memory. If you leave the cache enabled, all data will still be captured and decoded but you may lose unexecuted-prefetch flagging or synchronization with the execution trace. To capture four-cycle burst transfers you must leave the cache enabled. This will allow you to view all data coming across the bus, although some of the execution trace information will be lost.

The cache can be disabled with software by setting CR0.CD, TR12.CI, or the PCD bits in the page table entries to "1". It can be disabled in hardware by deasserting KEN#.

If the execution tracing enable bit (bit 1) in TR 12.C1 is set to 1, the branch trace message cycles will be captured and decoded by the logic analyzer. This will allow the trace to indicate that branches have occurred, even with the cache enabled.

5. If possible, you may want to disable page translation so that the physical addresses that the preprocessor interface monitors are effectively the logical addresses. Page translation can be disabled by setting CR0.PG to zero.

### Connecting to the HP E2443B

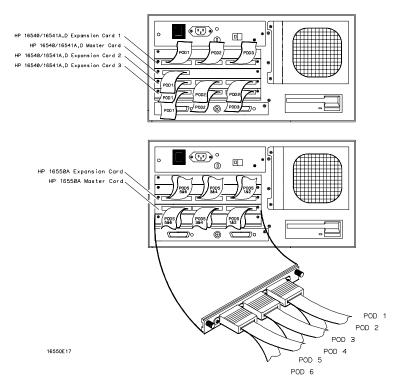

Connect the logic analyzer probes to the cable connectors of the preprocessor interface board as listed in table 1-3. Figure 1-2 shows the relative locations of the logic analyzer cards.

Figure 1-2. Logic Analyzer Card Locations (relative locations, actual slots used can vary)

### Power Up / Down Sequence

When powering up, the logic analyzer must be powered up first, and then the target system. The logic analyzer provides the power to the active circuits on the preprocessor interface; unpowered circuits may cause improper operation of the target system.

When powering down, power down the target system first, and then the logic analyzer.

HP E2443B Pentium CPU Preprocessor Interface Setting Up the HP E2443B

1-9

Table 1-3. Connections and Configuration Files

| HP 16540/16541A,D<br>Logic Analyzer | HP 16550A<br>Logic Analyzer | HP 1660A<br>Logic Analyzer | (Into) | HP E2443B                   |

|-------------------------------------|-----------------------------|----------------------------|--------|-----------------------------|

| Pod *                               | Pod **                      | Pod                        |        | Connector                   |

| Master Card, Pod 1                  | Master Card, Pod 3          | Pod 1                      |        | P1 (STAT) Clk1 <sup>↑</sup> |

| Exp. Card 3, Pod 3                  | Master Card, Pod 4          | Pod 2                      |        | P2 (STAT)                   |

| Exp. Card 3, Pod 1                  | Master Card, Pod 5          | Pod 3                      |        | P3 (ADDR)                   |

| Exp. Card 3, Pod 2                  | Master Card, Pod 6          | Pod 4                      |        | P4 (ADDR)                   |

| Exp. Card 2, Pod 1                  | Expander Card, Pod 1        | Pod 5                      |        | P5 (DATA)                   |

| Exp. Card 2, Pod 2                  | Expander Card, Pod 2        | Pod 6                      |        | P6 (DATA)                   |

| Exp. Card 1, Pod 1                  | Expander Card, Pod 3        | Pod 7                      |        | P7 (DATA_B)                 |

| Exp. Card 1, Pod 2                  | Expander Card, Pod 4        | Pod 8                      |        | P8 (DATA_B)                 |

| Exp. Card 2, Pod 3                  | Expander Card, Pod 5        |                            |        | P9 (additional status)      |

| Exp. Card 1, Pod 3                  | Expander Card, Pod 6        |                            |        | P10 (additional status)     |

|                                     |                             |                            |        |                             |

| CPENT_1                             | CPENT_2                     | CPENT_3                    |        |                             |

<sup>\*</sup> For the HP 16541A,D cards, expansion card 1 is the physically highest HP 16541A,D card, expansion card 2 is the second physically highest HP 16541A,D card, and expansion card 3 is the third highest HP 16541A,D card (see fig. 1-2).

<sup>\*\*</sup> For the HP 16550A cards, the Master Card is the lower card, and the expansion card is the higher card. Note that the two HP 16550A cards must be configured as a single logic analyzer.

### Setting Up the Analyzer from the Disk

The logic analyzer can be configured for Pentium CPU analysis by loading the appropriate configuration file. Loading this file will also load a default inverse assembler file (IAPENT or IAPENTE). To load the configuration and inverse assembler:

- Install the flexible disk in the front disk drive of the logic analyzer. (The HP 16500B mainframe has a hard disk drive. You can create a directory on the hard drive and copy the files from the flexible disk into the directory. For step two, select "Hard Disk.")

- 2. Select the System Front Disk menu.

- 3. Configure the menu to "Load" the analyzer configuration from disk.

- 4. Select the appropriate module (such as "100/500 MHz LA" or "Analyzer") for the load.

- 5. Use the knob to select the appropriate configuration file (see table 1-3).

- 6. Execute the load operation to load the file into the logic analyzer.

There are three inverse assemblers in the HP E2443B software. Table 1-4 shows the default inverse assembler which is automatically loaded by the configuration files. It also shows the different logic analyzer configurations which are supported by each inverse assembler. Pages 2-14 and 2-18 contain additional information on the different inverse assemblers.

To load a different inverse assembler after the configuration file has been loaded, repeat steps 1 - 6 above, except that for step 5, select the desired inverse assembler.

Table 2-4. Inverse Assembler Compatibility

| Logic Analyzer /<br>Mainframe                               | IAPENT  | IAPENTE | IAPENTD |

|-------------------------------------------------------------|---------|---------|---------|

| HP 16500A<br>Mainframe                                      | default | no      | yes     |

| HP 16500B<br>Mainframe                                      | yes *   | default | yes     |

| HP 1660A<br>Logic Analyzer,<br>software V01.xx              | default | no      | yes     |

| HP 1660A<br>Logic Analyzer,<br>software V02.00<br>or higher | yes *   | default | yes     |

<sup>\*</sup> Although this inverse assembler supports these logic analyzers, it does not provide all the features available with IAPENTE.

### **Timing Analysis**

The configuration loaded for state analysis may also be used for timing analysis. In Timing mode, the signals are buffered by a 74FCT646AT, with a maximum buffer delay of 6.3 ns (minimum 2.0 ns), and a typical 1.0 ns skew. To configure the logic analyzer for timing analysis:

- 1. Set the switches for timing (see page 1-3).

- 2. Load the appropriate configuration file from the disk.

- 3. Select the Configuration menu of the logic analyzer.

- 4. Select the Type field and select Timing.

### **Analyzing the Intel Pentium CPU**

#### Introduction

This chapter provides reference information on the format specification and symbols configured by the HP E2443B software. It also provides information about the inverse assemblers and status encoding.

### Format Specification

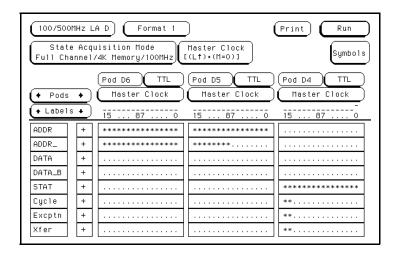

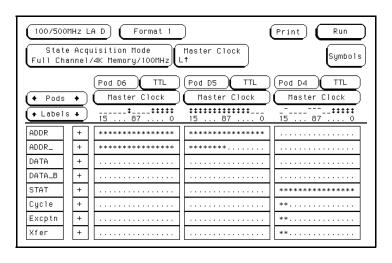

When you use the HP E2443B Preprocessor Interface, the format specification set up by the software will look similar to that shown in figure 2-1. There are some slight differences in the displays, according to which logic analyzer you are using. Table 3-1 in chapter 3 lists the Pentium CPU signals for the HP E2443B Preprocessor Interface and their corresponding lines to the logic analyzer.

The Setup/Hold time must remain in the current setting (4 ns setup/0 s hold for the HP 16540/16541A,D, 3.5 ns setup/0 s hold for the HP 1660A and HP 16550A) for proper operation with the HP E2443B.

Figure 2-1. Format Specification

HP E2443B

Pentium CPU Preprocessor Interface

Analyzing the Intel Pentium CPU

### **Symbols**

The configuration files set up symbol tables in the logic analyzer. The tables contain alphanumeric values which identify data patterns or ranges.

Table 2-1 lists the bits in the STAT label. Table 2-2 lists the additional status bits which are available on pods 9 and 10. Table 2-3 lists the additional status bits which are available on the HP 1660A and HP 16550A Logic Analyzers. Table 2-4 lists the signals which are available on the 2 x 4 header. Table 2-5 lists the symbols for the Cycle label. Table 2-6 lists the symbols for the Excptn label, and table 2-7 lists the symbols for the Xfer label. Table 2-8 lists the symbols for BE# . There are also symbols for many of the status signals (listed below table 2-8). The patterns for each symbol listed in the tables are shown in the binary base. In the actual software, these patterns may be listed in the hexadecimal base to conserve display space.

Table 2-1. STAT Label Bits

| Pod / Bit  | Status Signals | Description                                                                                                            |

|------------|----------------|------------------------------------------------------------------------------------------------------------------------|

| P1 / 7 - 0 | BE7 - BE0      | Byte Enable signals for the data bus.                                                                                  |

| P1/8       | IBT            | A high indicates a branch was taken.                                                                                   |

| P1/9       | KEN#           | A low on this signal indicates that the current cycle is cacheable, and will therefore be a burst.                     |

| P1 / 10    | CACHE#         | A low on this signal indicates internal cacheability of the cycle (for reads) or a burst writeback cycle (for writes). |

| P1 / 11    | W/R#           | A low indicates read and a high indicates write.                                                                       |

| P1 / 12    | D/C#           | A low indicates a code/special cycle and a high indicates a data cycle.                                                |

| P1 / 13    | M/IO#          | A low indicates an I/O cycle and a high indicates a memory cycle.                                                      |

| P1 / 14    | LOCK#          | A low indicates that the current bus cycle is locked.                                                                  |

| P1 / 15    | A20M#          | A low indicates an Address-bit 20 mask for internal cache lookups or memory cycles.                                    |

Analyzing the Intel Pentium CPU 2-2

HP E2443B Pentium CPU Preprocessor Interface

Table 2-1. STAT Label Bits (continued)

| Pod / Bit    | Status Signals | Description                                                                                                                                       |

|--------------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| P2/0         | Valid          | This signal is generated by the preprocessor interface. A high indicates that a data transfer is valid.                                           |

| P2 / 1       | ADS#           | A low indicates that a new valid bus cycle is being driven by the Pentium CPU.                                                                    |

| P2/2         | NA#            | A low indicates that the external memory is ready to accept a new bus cycle, although all data transfers for the current cycle are not completed. |

| P2/3         | BRDY#          | A low indicates valid data on the data pins.                                                                                                      |

| P2 / 4       | BRDYC#         | A low indicates valid data on the data pins for cacheable data.                                                                                   |

| P2/5         | PRDY           | A high indicates that the Pentium CPU is ready to accept a Probe Mode instruction.                                                                |

| P2/6         | AHOLD          | A high indicates an address hold request.                                                                                                         |

| P2/7         | EADS#          | A low indicates a valid external address has been driven onto the Pentium CPU address pins to be used for an inquiry cycle.                       |

| P2/8         | HIT#           | This signal indicates the outcome of the most recent inquire cycle.                                                                               |

| P2/9         | HITM#          | A low indicates (during inquire cycles) that a hit to a modified line in the data cache has occurred.                                             |

| P2 / 13 - 10 | BT3 - BT0      | Branch target address bits.                                                                                                                       |

| P2 / 14      | BOFF#          | A low indicates that the Pentium CPU should abort all outstanding bus cycles and float its bus on the next cycle.                                 |

| P2 / 15      | HLDA           | A high indicates that the Pentium CPU has acknowledged a hold request, and given up the bus.                                                      |

HP E2443B Pentium CPU Preprocessor Interface Analyzing the Intel Pentium CPU 2-3

**Table 2-2. Additional Status Bits**

| Pod / Bit | Status Signals | Description                                                                                                                                                           |

|-----------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P9/0      | R/S#           | A low indicates that the normal execution of the CPU has been stopped and placed into an idle state, possibly for execution of Boundary Scan/Probe Mode instructions. |

| P9/1      | ADSC#          | Address strobe used in chip-set mode.                                                                                                                                 |

| P9/2      | HOLD           | A high indicates a system bus hold request.                                                                                                                           |

| P9/3      | BREQ           | A high indicates that the Pentium CPU has internally generated a bus request.                                                                                         |

| P9/4      | INTR           | A high indicates an external interrupt.                                                                                                                               |

| P9/5      | NMI            | A high indicates a non-maskable external interrupt.                                                                                                                   |

| P9/6      | SCYC           | A high indicates a split cycle (more than two cycles will be locked together).                                                                                        |

| P9/7      | BUSCHK#        | A low indicates that the system has unsuccessfully completed a bus cycle.                                                                                             |

| P9/8      | FLUSH#         | A low indicates that the Pentium CPU will writeback all modified lines and invalidate its cache.                                                                      |

| P9/9      | INV            | Indicates the final cache line state for an inquire cycle hit.                                                                                                        |

| P9 / 10   | EWBE#          | A high (inactive) indicates that a write through cycle is pending in the external system.                                                                             |

| P9 / 11   | WB/WT#         | A low indicates that the current cache line is write-through, and a high indicates write-back.                                                                        |

| P9 / 12   | PWT            | Indicates cache writeback on a page-by-page basis.                                                                                                                    |

| P9 / 13   | PCD            | Indicates cacheability on a page-by-page basis.                                                                                                                       |

| P9 / 14   | RESET          | A high indicates that the Pentium CPU will begin execution from a known reset state.                                                                                  |

| P9 / 15   | INIT           | A high indicates that the Pentium CPU will begin execution from a known reset state, except the internal caches and some register values are left unchanged.          |

Analyzing the Intel Pentium CPU 2-4

HP E2443B Pentium CPU Preprocessor Interface

Table 2-2. Additional Status Bits (continued)

| Pod / Bit   | Status Signals | Description                                                                                         |

|-------------|----------------|-----------------------------------------------------------------------------------------------------|

| P10 / 7 - 0 | DP7 - 0        | Data parity pins.                                                                                   |

| P10 / 8     | IU             | A high indicates that an instruction in the u-pipeline has complete execution.                      |

| P10/9       | IV             | A high indicates that an instruction in the v-pipeline has complete execution.                      |

| P10 / 10    | SMI#           | A low indicates a System Power Management interrupt.                                                |

| P10 / 11    | SMIACT#        | A low indicates that the Pentium CPU is operating in System Management mode.                        |

| P10 / 12    | PM0/BP0        | BP are the breakpoint pins that indicate a breakpoint                                               |

| P10 / 13    | PM1/BP1        | match with the debug registers DR3 - 0 when they are programmed as such; the PM are the performance |

| P10 / 14    | BP2            | monitoring pins.                                                                                    |

| P10 / 15    | BP3            |                                                                                                     |

Table 2-3. Additional Status Bits (HP 1660A and HP 16550A only)

| Pod / Bit  | Signals  | Description                                                                                                                                                                                               |

|------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P3 / Clk1  | FERR#    | A low indicates that an unmasked floating point error has occurred.                                                                                                                                       |

| P4 / Clk1  | IERR#    | A low indicates either an internal parity error or a functional redundancy error.                                                                                                                         |

| P5 / Clk1  | IGNNE#   | A low partially indicates that the Pentium CPU will ignore any pending unmasked numeric exception and continue executing floating point instructions for the entire duration that the signal is asserted. |

| P6/Clk1    | PEN#     | This signal partially determines whether a machine check exception will be taken as a result of a parity error on a read cycle.                                                                           |

| P7 / Clk1  | PCHK#    | This signal indicates the result of a parity check on a read cycle.                                                                                                                                       |

| P8 / Clk1  | AP       | Address Parity for the address bus.                                                                                                                                                                       |

| P9 / Clk1  | * APCHK# | A low indicates a parity error on the address bus.                                                                                                                                                        |

| P10 / Clk1 | * FRCMC# | A low indicates that the Pentium CPU has been configured in checker mode, while a high indicates that the Pentium CPU has been configured in master mode.                                                 |

<sup>\*</sup> These signals are not available on the HP 1660A Logic Analyzer.

These signals are only available on the HP 1660A and HP 16550A Logic Analyzers. Each signal has its own label in the display.

Table 2-4. 2 x 4 Header Pins (JTAG)

| Signals * | Description                |

|-----------|----------------------------|

| TCK       | Test logic clock signal.   |

| TDI       | Test logic serial input.   |

| TDO       | Test logic serial output.  |

| TMS       | Test logic control signal. |

| TRST      | Test logic reset signal.   |

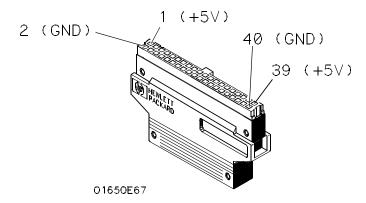

<sup>\*</sup> These signals are located on the  $2 \times 4$  header (see figure 1-1).

The Cycle symbols consist of the following signals, in the designated groupings:

(HLDA BOFF#) (LOCK# M/IO# D/C# W/R#) (BE7-4#) (BE3-0#)

Table 2-5. Cycle Symbols

| Symbol       | Pattern                       |

|--------------|-------------------------------|

| HLDA & BOFF  | 10 xxxx xxxx xxx              |

| Hold Ack     | 11 xxxx xxxx xxxx             |

| Bus Backoff  | 0 0                           |

| Int Ack 1st  | 0 1 x 0 0 0 1 1 1 0 1 1 1 1   |

| Int Ack 2nd  | 0 1 x 0 0 0 1 1 1 1 1 1 0     |

| I/O Read     | 0 1 1 0 1 0 x x x x x x x x   |

| I/O Write    | 0 1 1 0 1 1                   |

| Lckd Read    | 01 0010 xxxx xxxx             |

| Lckd Write   | 01 0011 хххх хххх             |

| Code Read    | 01 1100 xxxx xxxx             |

| Lckd Code Rd | 0 1 0 1 0 0 x x x x x x x x   |

| Reserved     | 01 x101 xxxx xxxx             |

| Mem Read     | 0 1 1 1 1 0 x x x x x x x x   |

| Mem Write    | 0 1 1 1 1 1 1 x x x x x x x x |

| Lckd Mem Rd  | 0 1 0 1 1 0 x x x x x x x x   |

| Lckd Mem Wr  | 0 1 0 1 1 1 x x x x x x x x   |

| Shutdown     | 01 x001 xxxx xxx0             |

| Flush        | 0 1 x 0 0 1 x x x x x x x 0 x |

| Halt         | 0 1                           |

| Writeback    | 0 1                           |

| Flush Ack    | 01 x001 xxx0 xxxx             |

| Brch Trg Msg | 01 x001 xx0x xxxx             |

| Undf Special | 0 1 x 0 0 1 x x x x x x x     |

|              | x x x x x x x x x x x x x     |

The Excptn symbols consist of the following signals, in the designated groupings:

(HLDA BOFF#) (D7-0) (M/IO# D/C# W/R#) (BE7-0#)

Table 2-6. Excptn Symbols

| Symbol                                                                    |                                 | Pattern                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |             |

|---------------------------------------------------------------------------|---------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| Int Ack 1st Cycl                                                          | 0 1                             | x x x x x x x x x 0 0 0 1 1 1 0 1 1 1 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 1           |

| 0:Divide Error<br>1:Debug Excptn<br>2:NMI Interrupt<br>3:Breakpoint       | 0 1<br>0 1<br>0 1<br>0 1        | 0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1 | 0<br>0      |

| 4:INTO Overflow<br>5:BOUND Rng Exc<br>6:Invalid Opcode<br>7:Dev Not Avail | 0 1<br>0 1<br>0 1<br>0 1        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 0<br>0      |

| 8:Double Fault<br>10:Inv Task SSeg<br>11:Seg N/Present<br>12:Stack Fault  | 0 1<br>0 1<br>0 1<br>0 1        | 0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1 | 0<br>0      |

| 13:Gen Protectn<br>14:Page Fault<br>16:Flt Point Err<br>17:Alignment Chk  | 0 1<br>0 1<br>0 1<br>0 1<br>x x | 0 0 0 0 1 1 0 1       0 0 0 0       1 1 1 1 1 1 1 1 0         0 0 0 0 1 1 1 0       0 0 0 0       1 1 1 1 1 1 1 1 1 1 1         0 0 0 1 0 0 0 0       0 0 0 0       1 1 1 1 1 1 1 1 1 1 1         0 0 0 1 0 0 0 0 1       0 0 0 0       1 1 1 1 1 1 1 1 1 1 1         x x x x x x x x x x x x x x x x x x x                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 0<br>0<br>0 |

HP E2443B Pentium CPU Preprocessor Interface Analyzing the Intel Pentium CPU 2-9

HLDA BOFF# W/R# CACHE# KEN#

Table 2-7. Xfer Symbols

| Symbol    | Pattern   |

|-----------|-----------|

| 1 Xfer Rd | 0 1 0 1 x |

| 1 Xfer Rd | 0 1 0 x 1 |

| 4 Xfer Rd | 0 1 0 0 0 |

| 1 Xfer Wr | 0 1 1 1 x |

| 4 Xfer Wr | 0 1 1 0 x |

|           | x x x x x |

Table 2-6. BE# Symbols

| Symbol                                                                    | Pattern                                           |

|---------------------------------------------------------------------------|---------------------------------------------------|

| 64/b7:0                                                                   | 0 0 0 0 0 0 0                                     |

| 32/b3:0<br>32/b4:1<br>32/b5:2<br>32/b6:3<br>32/b7:4                       | 1 1 1 1 0 0 0 0<br>1 1 1 0 0 0 0 1<br>1 1 0 0 0 0 |

| 16/b1:0<br>16/b2:1<br>16/b3:2<br>16/b4:3<br>16/b5:4<br>16/b6:5<br>16/b7:6 | 1 1 1 1 1 1 0 0 1 1 1 1 1 0 0 1 1 1 1 1           |

| 8/b0<br>8/b1<br>8/b2<br>8/b3<br>8/b4<br>8/b5<br>8/b6<br>8/b7              | 1 1 1 1 1 1 0 1 1 1 1 0 1 1 1 1 1 0 1 1 1 1 1     |

| None<br>                                                                  | 1 1 1 1 1 1 1 1 1 x x x x x x x x x               |

### Additional Symbols

There are also symbols for the following signals: KEN#, CACHE#, W/R#, D/C#, M/IO#, LOCK#, SCYC, IBT, IV, IU, WB/WT#, PWT, PCD, BUSCK#, FLUSH#, IERR#, INTR, NMI, SMI#, SMIAC#, A20M#, AP, APCHK#, ADS#, AHOLD, BOFF#, BRDY#, BRDYC#, EADS#, EWBE#, HIT#, HITM#, HLDA, HOLD, INV, NA#, BREQ, RESET, INIT, PEN#, PCHK#, FERR#, IGNNE#, PRDY, and R/S#.

HP E2443B Pentium CPU Preprocessor Interface Analyzing the Intel Pentium CPU 2-11

### **Listing Menu**

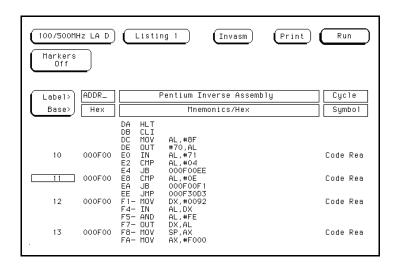

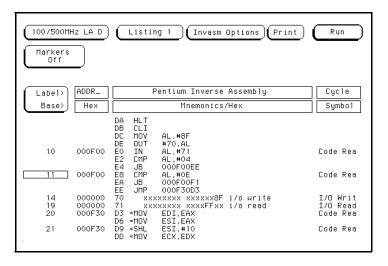

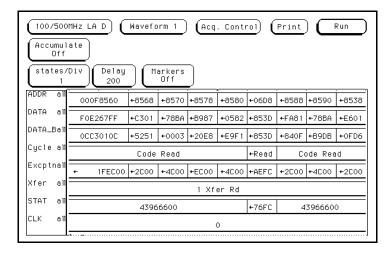

Captured data is displayed as shown in figure 2-2 (with the IAPENT inverse assembler) or figure 2-3 (with the IAPENTE inverse assembler). The inverse assemblers are constructed so the mnemonic output closely resembles the actual assembly source code. In figure 2-3, the unexecuted prefetches have been suppressed.

The logic analyzers always probe the full 64-bit data bus of the Pentium CPU. When fewer than the full 64 bits of the data bus are used by a memory cycle, the inverse assembler marks the bytes not used by the microprocessor with "xx."

Figure 2-2. State Listing, IAPENT Inverse Assembler

Figure 2-3. State Listing, IAPENTE Inverse Assembler (Unexecuted Prefetches Suppressed)

### Burst and Cacheable Data

The logic analyzer can track burst (4-transfer) and non-burst (1-transfer) cycles. During burst transfers the microprocessor holds the address constant during the entire burst. The inverse assembler listing displays the two least significant hexadecimal digits of the actual address (derived by the inverse assembler) at the left side of the column.

Up to eight instructions may be displayed for a single analyzer state, because the Pentium CPU fetches eight instruction bytes from program memory. If the first byte of these eight bytes contains a single-byte instruction, the next sequential instruction begins in the next higher byte. This process continues from the least significant byte to the most significant byte until all of the fetched bytes are used. When a single state contains more than one instruction, each instruction is displayed on a separate line.

## The Pentium CPU Inverse Assemblers

The HP E2443B Preprocessor Interface software contains three inverse assemblers. There are two default inverse assemblers, IAPENT and IAPENTE, and a data-mode inverse assembler, IAPENTD. IAPENTE contains additional features which use the increased capabilities of some of the logic analyzers (only available with the HP 16500B mainframe, and the HP 1660A Logic Analyzer with software version V02.00 or higher). For more information on the IAPENTE features, see "The IAPENTE Inverse Assembler" in this chapter.

The default inverse assemblers analyze the microprocessor code and disassemble it into Pentium CPU mnemonics, which are displayed on the logic analyzer screen. Unexecuted prefetches are marked with a hyphen (-).

The data-mode inverse assembler (IAPENTD) functions like the default inverse assemblers, except that it does not decode instructions or mark unused prefetches. IAPENTD is useful for examining data flow, while IAPENT or IAPENTE are useful for examining instruction flow. You can also store data, and re-examine it later using a different inverse assembler.

The inverse assemblers only work in State-Per-Transfer and Debugger modes. They do not work in State-Per-Clock or Timing modes.

#### **Address Labels**

Two different address labels are provided, ADDR and ADDR\_. ADDR provides the full 32 address bits (A31:0), while ADDR\_ provides the upper 24 address bits (A31:8).

When using the inverse assembler, use ADDR\_ in the listing. ADDR\_ gives you the upper 24 bits of the address, while the inverse assembler display gives you the lower eight address bits (A7:0) in its first two columns. Using these two fields together gives you the entire 32 address bits.

The ADDR label displays the actual (acquired) 32-bit address, with A2:0 = 000 binary. When the inverse assembler is turned off, the ADDR field can be used to display the full address in hexadecimal format.

Analyzing the Intel Pentium CPU 2-14

HP E2443B Pentium CPU Preprocessor Interface

### Prefetched Instructions

The Pentium CPU microprocessor is a prefetching microprocessor. It may prefetch up to 64 bytes (eight 64-bit code fetches) before the current opcode. When a program executes an instruction that causes a branch, the prefetched code is not used and will be discarded by the microprocessor. The inverse assembler marks unused prefetches with a hyphen "—" in the third column of the display.

The logic analyzer captures prefetches, even if they are not executed. Therefore, care must be taken when you are specifying a trigger condition or a storage qualification and the instruction of interest follows an instruction that may cause branching. An unused prefetch may generate an unwanted trigger.

The Pentium CPU has a prefetch queue of essentially 64 bytes. This means that by the time a branching instruction is fully decoded, up to 64 other instruction bytes may have already been prefetched across the data bus, and stored in the logic analyzer. Both exceptions and instructions can cause the prefetch queue to be flushed and subsequently refilled. Branches, jumps, calls, returns, and system control instructions are the most common causes of prefetch queue flushes, but there are many others. Refer to your Pentium CPU user's manual for more information.

### Synchronizing the Inverse Assembler

In some cases the prefetch marking algorithm in the inverse assembler may lose synchronization, and unused prefetches or executed instructions may be incorrectly marked. If you suspect that the inverse assembler has lost synchronization, re-synchronize the inverse assembler by pointing to an executed instruction. Once synchronized, the inverse assembler will disassemble from this state through the end of the screen. To point to an executed instruction:

- 1. Select a line on the display that you know contains the first byte of an executed instruction.

- 2. Roll this line to the top of the listing.

The cursor location is not the top of the listing. In figure 2-2, the instruction DA HLT is the top of the listing.

3. For the IAPENT or IAPENTD inverse assemblers, select the "Invasm" field at the top of the display. A pop-up appears with the following choices:

| Size 16 Byte 0/8 | Size 32 Byte 0/8 |

|------------------|------------------|

| Size 16 Byte 1/9 | Size 32 Byte 1/9 |

| Size 16 Byte 2/A | Size 32 Byte 2/A |

| Size 16 Byte 3/B | Size 32 Byte 3/B |

| Size 16 Byte 4/C | Size 32 Byte 4/C |

| Size 16 Byte 5/D | Size 32 Byte 5/D |

| Size 16 Byte 6/E | Size 32 Byte 6/E |

| Size 16 Byte 7/F | Size 32 Byte 7/F |

For the IAPENTE inverse assembler, select the "Invasm Options" button, and use the "Code Synchronization" portion of the submenu.

Size, as used here, refers to the default operand size for this code (16 or 32 bits).

4. Select the choice that identifies which byte of the captured state contains the first byte of the code fetch and what the default operand size is for this code (16 or 32 bits). With the IAPENTE inverse assembler, also select "Align".

Analyzing the Intel Pentium CPU 2-16

HP E2443B Pentium CPU Preprocessor Interface

Rolling the screen up will inverse assemble the lines as they appear on the bottom of the screen. If you jump to another area of the acquisition buffer by entering a new line number, you may have to re-synchronize the inverse assembler by repeating steps 1 through 4.

#### **Operand Size**

The "= "symbol is displayed in the fourth column of the inverse assembly display for 32-bit operands. The "= "symbol will appear for default 32-bit operand operations, as well as for operations when the operand size prefix is encountered and decoded.

# Byte Enable Validity

The Byte Enables are not valid during cache accesses (bursts). Since all cache reads and writes must be 64 bits, all data lines are valid during these cycles.

# Incomplete Decoding

If a complete opcode is not present, the inverse assembler will not be able to decode it. A pair of asterisks "\*\*" will be listed on the display.

### Opcode Data Numeric Bases

Most data is displayed in hexadecimal format. An exceptions is the operand for the INT value, which is displayed in decimal. Decimal numbers are indicated by a "d" suffix.

### Branch Trace Messaging

The Pentium CPU inverse assemblers decode branch trace messages, which gives you branch target addresses. This is especially useful for tracing execution while operating out of cache.

### **Illegal Instructions**

When the inverse assembler decodes an illegal instruction, the message "Illegal Opcode" is displayed, along with the byte(s) which caused the decoded illegal opcode. This message is often an indication that the inverse assembler has lost synchronization (see page 2-16).

Do not modify the ADDR, DATA, DATA\_B, or STAT labels in the format specification if you want inverse assembly. Changes may cause incorrect results. Also note that if the trace specification is modified to store only selected bus cycles, incorrect or incomplete inverse assembly may result.

HP E2443B Pentium CPU Preprocessor Interface Analyzing the Intel Pentium CPU 2-17

# The IAPENTE Inverse Assembler

The IAPENTE inverse assembler contains additional features which use the increased capabilities of some of the logic analyzers. It supports the HP 16540/16541A,D and HP 16550A Logic Analyzers in the HP 16500B mainframe, and the HP 1660A Logic Analyzer with software version V02.00 or higher. For those logic analyzer systems, the IAPENTE inverse assembler is automatically loaded when the appropriate configuration file is loaded. Note that all the features in the IAPENT inverse assembler are also included in the IAPENTE inverse assembler (see previous section).

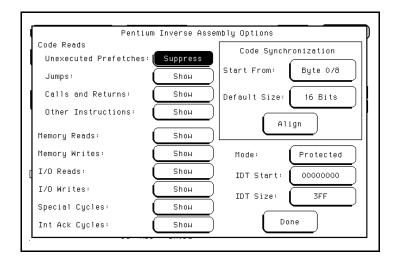

The IAPENTE Inverse Assembly Options menu contains three functions: display filtering with Show/Suppress selections, Code Synchronization, and IDT description entry (see figure 2-4). The following sections describe these functions.

If the X or O pattern markers are turned on, and the designated pattern is found in a state that has been Suppressed with display filtering, the following message will appear on the logic analyzer display: "X (or O) pattern found, but state is suppressed."

Figure 2-4. IAPENTE Inverse Assembly Options

#### **Show/Suppress**

The Suppress/Show settings determine whether the various microprocessor operations are shown or suppressed on the logic analyzer display. Figure 2-4 shows the microprocessor operations which have this option. The settings for the various operations do not affect the data which is stored by the logic analyzer, they only affect whether that data is displayed or not. The same data can be examined with different settings, for different analysis requirements.

This function allows faster analysis in two ways. First, unneeded information can be filtered out of the display. Figure 2-4 shows the settings to suppress unexecuted prefetches. Figure 2-3 (page 2-13) shows a listing with the unexecuted prefetches suppressed, so that only executed instructions are displayed. A comparison of figures 2-2 and 2-3 shows the difference in the listing display.

Second, particular operations can be isolated by suppressing all other operations. For example, I/O accesses can be shown, with all other operations suppressed, allowing quick analysis of I/O accesses.

# Code Synchronization

The Code Synchronization enables the inverse assembler to resynchronize with the microprocessor code. In some cases the prefetch marking algorithm in the inverse assembler may lose synchronization, and unused prefetches or executed instructions may be incorrectly marked. If any of the Code Reads are suppressed, this could cause some executed instructions to be missing from the display.

To resynchronize the inverse assembler, use the procedure on page 2-16.

### **IDT Description**

The IDT Description settings include Mode, IDT Start, and IDT Size. Mode can be Protected, Real, or Virtual. IDT Start refers to the starting address of the Interrupt Descriptor Table, and IDT Size refers to the size of the table. Set these functions to match the target system settings.

In most cases, the inverse assembler can automatically determine the target system settings, and will operate properly regardless of the settings entered. The inverse assembler uses the information from these settings only in cases of uncertainty. If you suspect that the inverse assembler is disassembling improperly, check that these settings match your target system.

HP E2443B Pentium CPU Preprocessor Interface Analyzing the Intel Pentium CPU 2-19

# Modes of Operation

The HP E2443B can capture Pentium CPU data in four modes; Timing, State-Per-Clock, State-Per-Transfer, and Debugger. In Timing mode, the signals are buffered, but otherwise passed straight through to the logic analyzer; in State-Per-Clock mode, all signals are latched by CLK, and clocked into the logic analyzer each CLK cycle. This allows the logic analyzer to capture wait states and idle states, in addition to valid data states. In State-Per-Transfer and Debugger modes, address pipelining is realigned, and only valid data transfers are clocked into the logic analyzer. Debugger mode is identical to State-Per-Transfer mode with the exception that, whenever IU, IV or IBT are asserted, data is captured regardless of whether or not it is valid.

Timing mode also allows a choice of buffered or phase-locked loop clocks (see Chapter 1). Chapter 1 shows the switch settings for selecting the different modes of operation.

### Qualified / Non-qualified Clocking

In non-qualified clocking, Clk1  $\uparrow$  (on the HP E2443B pod P1) is used to clock information into the logic analyzer. In qualified clocking, only those edges of Clk1  $\uparrow$  that occur when ClkQual is asserted will clock information into the logic analyzer. Therefore, qualified clocking allows you to filter information, since ClkQual must be asserted before the logic analyzer is clocked by Clk1  $\uparrow$ .

The logic analyzer must use qualified clocking for State-Per-Transfer and Debugger modes; it can be clocked as qualified or non-qualified for State-Per-Clock mode. With non-qualified clocking, every state is captured, regardless of the settings for the switches. The configuration file sets up the logic analyzer for qualified clocking.

To change to non-qualified clocking, use the Format menu to remove the clock qualifier. The clock qualifier is the M Clock on the HP 16550A, and the K Clock on the HP 16540/16541A,D and HP 1660A Logic Analyzers. Figure 2-5 shows the Format specification with the clock qualifier removed. Only the L Clock (Clk1) is shown in the Master Clock field. Clk1 is the L clock in the HP 16550A; it is the J clock in the HP 1660A and HP 16540/16541A.D.

#### ClkQual

In State-Per-Clock mode, six signals can be used as inputs to the clock qualifier (see Chapter 1). The inputs are selected by closing the appropriate switches. The only states which will be captured are those in which the signal for a selected (closed) switch is asserted. The equation for the clock qualifier in State-Per-Clock mode is: